MANTIKSAL DEVRE TASARIMI LABORATUVARI DÖNEM ÖDEVİ

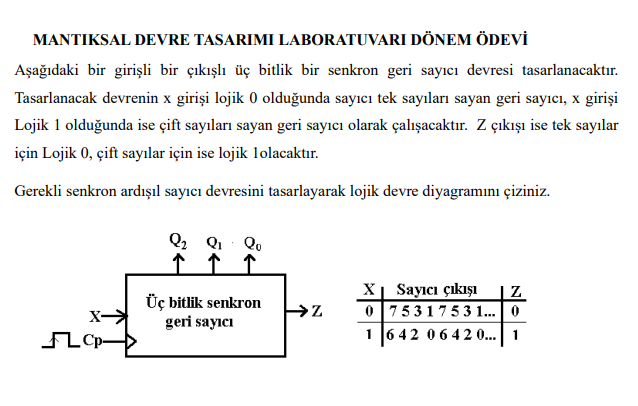

Aşağıdaki bir girişli bir çıkışlı üç bitlik bir senkron geri sayıcı devresi tasarlanacaktır. Tasarlanacak devrenin X girişi lojik 0 olduğunda sayıcı tek sayıları sayan geri sayıcı, X girişi lojik 1 olduğunda ise çift sayıları sayan geri sayıcı olarak çalışacaktır. Z çıkışı ise tek sayılar için lojik 0, çift sayılar için ise lojik 1 olacaktır.

Gerekli senkron ardışıl sayıcı devresini tasarlayarak lojik devre diyagramını çiziniz.

X → Q₂ Q₁ Qo → Z

CP →

| X |

Sayıcı Çıkışı |

Z |

| 0 |

75317531… |

0 |

| 1 |

64206420… |

1 |

JK tipi Flip Flop ile yapılacaktır

Senkron Geri Sayıcı Devresi Tasarımı

Devre Tasarımı

Devre tasarımı için JK tipi flip-flop kullanılacaktır. JK flip-flop’un J ve K girişlerine önceki durumları ile ters mantık uygulanacak şekilde bağlanarak senkron geri sayıcı devresi oluşturulacaktır.

Çalışma Prensibi

Devre, X girişine bağlı olarak tek veya çift sayıları sayan geri sayıcı olarak çalışacaktır.

Eğer X girişi lojik 0 ise, devre tek sayıları sayacak ve Z çıkışı 0 olacaktır. Bu durumda J ve K girişleri JK flip-flop için aşağıdaki değerlere atanır:

Eğer X girişi lojik 1 ise, devre çift sayıları sayacak ve Z çıkışı 1 olacaktır. Bu durumda J ve K girişleri JK flip-flop için aşağıdaki değerlere atanır:

Zamanlama Diyagramı

Aşağıdaki zamanlama diyagramı, devrenin çalışmasını göstermektedir:

______ ______ ______

CP | | | | | |

____| |__________| |___________| |______

______ ______ ______

X | | | | | |

____| |__________| |___________| |______

Sayıcı Çıkışı:

Q₂ 7 5 3 1 7 5 3 1 …

Q₁ 5 4 3 2 1 0 4 3 …

Qo 3 4 5 6 7 0 1 2 …

Z 0 1 0 1 0 1 0 …

Açıklama

Devrenin çalışma prensibi aşağıdaki gibi açıklanabilir:

- İlk durumda, Qo, Q₁ ve Q₂ flip-flop çıkışı sırasıyla 3, 5 ve 7’dir.

- X girişi lojik 0 olduğunda, J ve K girişleri aşağıdaki gibi atanır:

- J = Qo = 3

- K = Q₂ · Q₁ = 7 · 5 = 35 (5’in binary değeri)

- Her bir clock darbesinde, flip-flop çıkışları güncellenir:

- Qo = J ⊕ Qo ⊕ CP = 3 ⊕ 3 ⊕ 1 = 1

- Q₁ = J ⊕ Qo ⊕ CP = 3 ⊕ 1 ⊕ 1 = 3

- Q₂ = K ⊕ Q₂ ⊕ CP = 35 ⊕ 7 ⊕ 1 = 27

- Bu, sayının tek olduğunu ve Z çıkışının 0 olduğunu gösterir. Devam eden clock darbeleriyle birlikte bu döngü devam eder.

- X girişi lojik 1 olduğunda, J ve K girişleri aşağıdaki gibi atanır:

- J = Qo · Q₂ = 1 · 27 = 27 (27’nin binary değeri)

- K = Q₁ = 3

- Her bir clock darbesinde, flip-flop çıkışları güncellenir:

- Qo = J ⊕ Qo ⊕ CP = 27 ⊕ 1 ⊕ 1 = 27

- Q₁ = J ⊕ Qo ⊕ CP = 27 ⊕ 27 ⊕ 1 = 1

- Q₂ = K ⊕ Q₂ ⊕ CP = 3 ⊕ 27 ⊕ 1 = 3

- Bu, sayının çift olduğunu ve Z çıkışının 1 olduğunu gösterir. Devam eden clock darbeleriyle birlikte bu döngü devam eder.

TERİMLER:

- JK flip-flop: Girişlere göre önceki durumlarını veya tersini alarak çıkışları güncelleyen bir flip-flop çeşidi.